微信公众号:花生屋

关注可了解更多的知识和信息。问题或建议,请公众号留言。

ZYNQ-7000系列

Zynq®-7000 SoC 系列集成 ARM® 处理器的软件可编程性与 FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上高度集成 CPU、DSP、ASSP 以及混合信号功能。

简单来说就是把FPGA和ARM“粘”在一起了。

PL和PS数据交互

PL和PS的高效交互是ZYNQ 7000 soc 开发的重中之重。PS和PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现。PL端大量数据实时送到PS进行处理,或将PS端处理结果实时送到PL端处理,则可以通过DDR交换。

硬件设计

使用Vivado 2017.4测试

首先新建工程,这里不再赘述,按照开发板选择对应芯片即可。

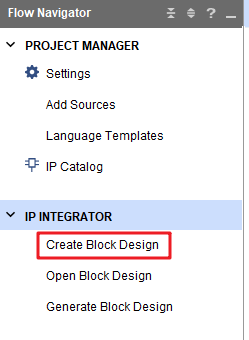

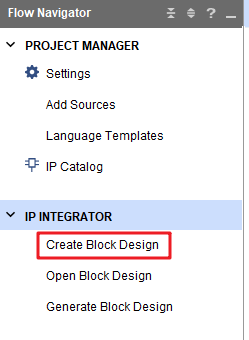

创建 Block Design。

创建 Block Design 创建 Block Design

添加ZYNQ处理器。

添加ZYNQ处理器

根据开发板原理图,设置串口接口,便于结果输出。

I/O设置

记住修改Bank1内部电压。

Bank1电压

修改对应的DDR型号。

修改DDR型号

配置完成后,点击 Run Block Automation 让 Vivado 自动完成布线,然后生成Bitstream。

软件设计

导出硬件信息,点击 File -> Export -> Export Hardware。

然后运行SDK,点击 File -> Launch SDK。

创建一个名为“ddr_test”的工程。

新建工程

对工程进行命名,然后点击下一步。

命名

选择hello world模板,然后点击完成。

选择模板

对程序进行修改:

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"

#include "xil_io.h"

#define DDR_BASEARDDR XPAR_DDR_MEM_BASEADDR + 0x10000000

int main()

{

init_platform();

print("Hello World\n\r");

for(int i = 0; i < 32; i++)

{

Xil_Out32(DDR_BASEARDDR + i*4, i);

}

for(int i = 0; i < 32; i++)

{

int rev = Xil_In32(DDR_BASEARDDR + i*4);

xil_printf("The address at %x data is: %x \r\n",DDR_BASEARDDR + i*4,rev);

}

cleanup_platform();

return 0;

}

之后下载、调试程序,可以在串口看到输出结果。

实验结果

|